# Design of Concurrent Dual Band Low Noise Amplifier for WLAN Applications

Anishaziela Azizan<sup>1,\*</sup>, Sohiful Anuar Zainol Murad<sup>1,2</sup>, Ahmad Fariz Hasan<sup>1,2</sup>, Asrulnizam Abd Manaf<sup>3</sup> and Prapto Nugroho<sup>4</sup>

<sup>1</sup> Faculty of Electronic Engineering & Technology (FKTEN), Universiti Malaysia Perlis (UniMAP) 02600, Arau Perlis, Malaysia

<sup>2</sup> Advanced Communication Engineering, Centre of Excellence (CoE), Faculty of Electronic Engineering & Technology (FKTEN), Universiti Malaysia Perlis (UniMAP), 02600, Arau Perlis, Malaysia

<sup>3</sup> School of Electrical and Electronic Engineering, Engineering Campus, Universiti Sains Malaysia, 14300, Nibong Tebal, Pulau Pinang, Malaysia

<sup>4</sup> Department of Electrical and Information Engineering, Faculty of Engineering, Universitas Gadjah Mada, 55281, Yogyakarta, Indonesia

|                                                                                | ABSTRACT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <i>Keywords:</i><br>Dual band; low noise amplifier; forward<br>body bias; WLAN | This paper presents a dual band LNA CMOS designed for a Wireless Local Area Network (WLAN) application using CMOS 0.13-µm Silterra technology. The proposed design incorporates forward body bias technique with cascode and notch filter configuration to achieve both low power consumption and high gain. The simulation results demonstrate a total power consumption of 2.39 mW at a low supply voltage of 0.5 V, with a gain of 16 dB at 2.4 GHz and 12 dB at 5.2 GHz. Additionally, input return loss of -12.3 dB and -14.2 dB with noise figures of 2.93 dBm and 4.23 dBm were obtained at 2.4 GHz and 5.2 GHz, respectively. Overall, this research contributes to the development of dual band LNA designs for WLAN applications. |

#### 1. Introduction

Wireless local area networks (WLANs) have seen significant growth and the demand for highperformance wireless devices has increased over the past few years. The design of a low noise amplifier (LNA) is critical to the overall operation of a WLAN system [1, 2]. Dual-band LNAs are useful in reducing the complexity and cost of WLAN systems while providing high-performance. These LNAs can operate at two frequency bands simultaneously and are particularly useful in WLAN applications that operate at different frequency bands, such as 2.4 GHz and 5.2 GHz.

The design of concurrent dual band low noise amplifiers (LNAs) is becoming increasingly important for modern wireless communication systems that require support for multiple frequency bands. However, designing a concurrent dual band LNA with good performance at both bands is a challenging task due to the conflicting design requirements of the two frequency bands. According to the study by [3, 4] one of the main challenges is achieving a good tradeoff between gain and noise figure in both frequency bands. Another challenge is minimizing the impact of process

\* Corresponding author.

https://doi.org/10.37934/araset.63.1.146152

E-mail address: anishaziela@unimap.edu.my

variations, which can lead to significant performance degradation in dual-band LNAs [5-7]. Recent design approaches have focused on improving the performance of dual-band LNAs while maintaining a compact circuit size and low fabrication cost. To achieve these goals, various circuit topologies and techniques have been proposed, including notch filter [8, 9], current-reuse [10, 11] and tunable matching networks [12, 13]. Despite the progress made in recent years, there are still several challenges that need to be addressed in the design of concurrent dual band LNAs. These include ensuring robustness against interference and signal distortion [2, 14] and achieving high linearity in both frequency bands [12, 15]. Furthermore, power dissipation has become a critical concern in most circuit design [16].

The goal of this study is to increase LNA performance and minimize power consumption by designing a concurrent dual band CMOS LNA at 2.4 GHz and 5.2 GHz utilizing forward body bias and the notch filter approach.

# 2. Design Methodology

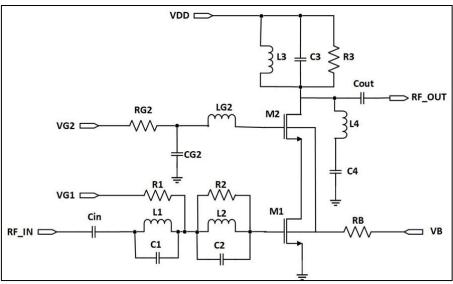

The proposed schematic design is illustrated in Figure 1. The design implementation is based on the forward body bias architecture, which ensures low power consumption through the ability of transistors to turn on at low supply voltage [17, 18]. Moreover, this technique is cost effective and straightforward. The proposed dual band LNA incorporates a cascode configuration as to enhance the gain [19, 20]. M1 is connected in a common source configuration by grounding the source, while the gate of M1 serves as the input port, and the drain of M2 is the output port for signals. Low power consumption is ensured by immediately lowering the threshold voltage (Vth) of NMOS transistors when the body terminal is connected to a voltage source.

The proposed LNA design implementation incorporates a biasing voltage (VB) of 0.3 V, significantly lower than the PN junction turn-on voltage of 0.7 V, resulting in negligible leakage current in the NMOS transistor's body-source junction. Figure 1 shows that R1 and RG2 are the biasing resistances of transistors M1 and M2 gates, respectively, while R2 is connected to L2 and C2 for input matching. The values of L3, C3, R3, L4 and C4 define output matching at 2.4 GHz and 5.2 GHz.

Transistor size is a key factor when trying to achieve low power consumption while maximizing gain and efficiency. The design implementation involves setting the size of the transistors to achieve optimal current consumption and acceptable gain. To guarantee adequate linearity and efficiency, the sizes of MI and M2 are adjusted to  $100 \mu m/0.13 \mu m$  and  $300 \mu m/0.13 \mu m$ , with 10 and 30 fingers, respectively. Additionally, the output matching is achieved through the notch filter technique in which parallel RLC circuit of R3, C3, and L3 and series LC circuit of C4 and L4 which are tuned to match the desired values at center frequencies of 2.4 GHz and 5.2 GHz.

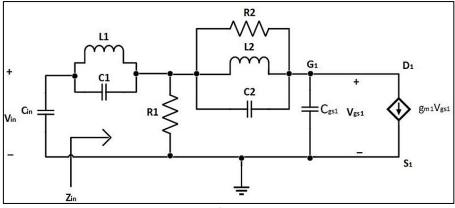

The small signal model illustrated in Figure 2 was employed to determine the input matching of the dual band LNA under consideration. The input impedance calculation are as follows.

$$Z_{in} = Z_{CGS1} + \begin{pmatrix} R_2 \parallel & Z_{L2} \parallel & Z_{C2} \end{pmatrix} + \begin{pmatrix} R_1 \parallel & \left( \begin{pmatrix} Z_{L1} \parallel & Z_{C1} \end{pmatrix} + Z_{Cin} \end{pmatrix} \right)$$

(1)

$$Z_{in} = \frac{1}{jwCGS1} + \begin{pmatrix} R_2 \parallel & jwL2 \parallel & \frac{1}{jwC2} \end{pmatrix} + \begin{pmatrix} R_1 \parallel & \left( \begin{pmatrix} jwL1 \parallel & \frac{1}{jwC1} \end{pmatrix} + \frac{1}{jwCin} \end{pmatrix}$$

(2)

Fig. 1. The proposed schematic of dual band LNA for 2.4 GHz and 5.2 GHz

Fig. 2. A small signal model for calculating input impedance

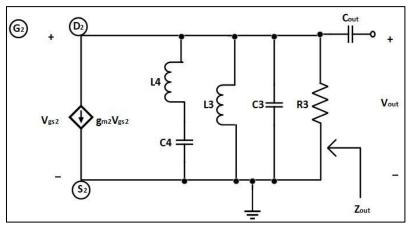

Additionally, the output matching network of the LNA was depicted in Figure 3, which comprises a series connection of bandpass and band stop filter networks. The inductor and capacitor circuits were resonating at the intended operating frequencies of 2.4 GHz and 5.2 GHz. Consequently, the output impedance for this design can be expressed as a function of the input matching and LC components.

$$Z_{0} = Z_{L3} \parallel Z_{C3} \parallel Z_{R3} + Z_{L4} + Z_{C4}$$

$$Z_{0} = \left( jwL3 \parallel \frac{1}{jwC3} \parallel R3 \right) + jwL4 + \frac{1}{jwC4}$$

(3)

(4)

Fig. 3. A small signal model for calculating output impedance

#### 3. Results

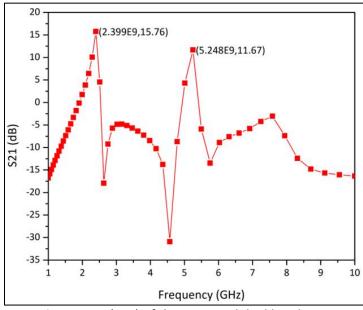

This section shows the results of the suggested dual band LNA design, which uses the forward body bias approach to minimize the threshold voltage and, as a result, power consumption. Furthermore, at 2.4 and 5.2 GHz, the notch filter approach guarantees good input and output matching. The results of the post-layout simulation show that the dual band LNA achieves a low power consumption of 2.39 mW from a 0.5 V power source while retaining acceptable parameters.

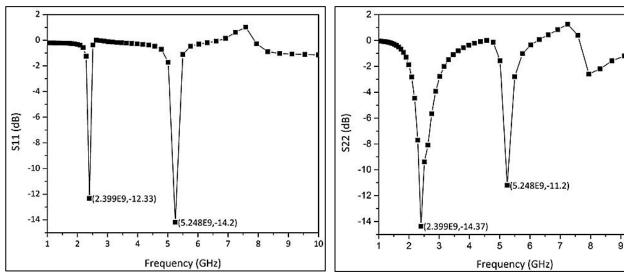

Figure 4 depicts the voltage gain (S21) of the dual-band LNA's forward body bias with cascode variants. According to simulation results, S21 is 15.76 dB at 2.4 GHz and 11.67 dB at 5.2 GHz. However, parasitic effects, notably parasitic resistance in load inductors, have an influence on the circuit's gain. Figure 5 depicts the simulation results of the suggested LNA's input matching. The pre-layout input return loss (S11) at 2.4 GHz is -12.3 dB, whereas it is -14.2 dB at 5.2 GHz, which can be ascribed to parasitic effects such as inductor-substrate parasitic and input capacitance. The input matching value, on the other hand, is judged acceptable and falls within the desired range. Figure 6 depicts the output matching of the proposed dual band LNA. Figure 6 shows the output matching of the proposed dual band LNA. Figure 6 shows the output matching of the proposed dual-band LNA, which reveals a simulated S22 of -14.37 dB at 2.4 GHz and -11.2 dB at 5.2 GHz.

Fig. 4. Gain (S21) of the proposed dual band LNA

Fig. 5. Input return loss (S11) of the proposed dual band LNA

Fig. 6. Output return loss (S22) of the proposed dual band LNA

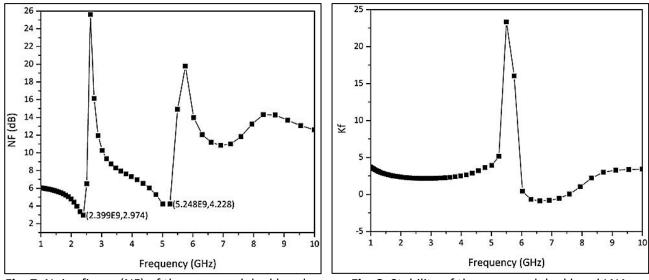

The pre-layout results for noise figure are depicted in Figure 7. The circuit achieves an NF of 2.97 dB and 4.22 dB at 2.4 GHz and 5.2 GHz, respectively. While the achieved NF is within specification, there is room for optimization. Figure 8 illustrates the stability factor plot. The LNA remains unconditionally stable, with stability values exceeding 1 for both frequencies.

Fig. 7. Noise figure (NF) of the proposed dual band LNA

Fig. 8. Stability of the proposed dual band LNA

Table 1 compares previously reported dual band LNAs with these findings. A cascode arrangement was used to increase gain in [1]. [10] used the cascode common source inductive degeneration architecture to accomplish power restricted simultaneous noise and input matching at 2.4 and 5.2 GHz. [18] used the LC parallel resonance and LC series networks to accomplish dual band input impedance matching and noise matching using a small-size capacitor and linked inductor for gain improvement. [19] used the current-reuse approach to decrease power dissipation. Finally, in [20], a linearization approach was applied to improve the input third-order intercept point (IIP3), and an enhanced output matching network was built for wireless and

Bluetooth applications utilising 65 nm CMOS technology. This suggested dual band LNA has a lower power consumption of 2.39 mW with a low supply voltage while keeping comparable other metrics.

| Parameter           | [1]* | [10]  | [19]* | [21]  | [22]  | This work |

|---------------------|------|-------|-------|-------|-------|-----------|

|                     |      |       |       | • •   |       |           |

| CMOS Technology(µm) | 0.13 | 0.13  | 0.13  | 0.18  | 0.65  | 0.13      |

| Frequency (GHz)     | 2.4  | 2.4   | 2.4   | 2.4   | 2.4   | 2.4       |

|                     | 5.2  | 5.2   | 5.2   | 5.2   | 5.2   | 5.2       |

| Supply Voltage (V)  | 1.2  | 1.2   | 1.2   | 1.5   | 1.0   | 0.5       |

| S21 (dB)            | 21.8 | 19.3  | 17.1  | 15.1  | 14.24 | 15.8      |

|                     | 14.2 | 17.5  | 8.5   | 13    | 11    | 11.7      |

| S11 (dB)            | -18  | -16.8 | -15.6 | -13.3 | -24.3 | -12.3     |

|                     | -16  | -19.4 | -13.8 | -12.4 | -26.4 | -14.2     |

| S22 (dB)            | -14  | -23.5 | N/A   | N/A   | N/A   | -14.4     |

|                     | -16  | -27.8 | N/A   | N/A   | N/A   | -11.2     |

| IIP3 (dBm)          | 7    | -20.1 | N/A   | -16   | -1.66 | -12.4     |

|                     | 10   | -18.1 | N/A   | -10   | 0.04  | -20       |

| NF (dB)             | 4.1  | 3.2   | 3.6   | 2.7   | 2.4   | 2.97      |

|                     | 5.0  | 3.3   | 3.3   | 3.2   | 4.5   | 4.23      |

| Power (mW)          | 32.9 | 2.4   | 9.8   | 2.49  | 3.6   | 2.39      |

\*post-layout simulation

# 4. Conclusions

This study emphasises the use of the forward body bias approach to reduce threshold voltage, resulting in a considerable reduction in power usage. A notch filter approach is also used to produce good input-output matching at 2.4 and 5.2 GHz. According to pre-layout simulation findings, the suggested dual-band LNA consumes 2.39 mW from a 0.5 V power source. Overall, the results show that the parameters are acceptable and that WLAN applications have promise.

# Acknowledgement

This research was funded by Universiti Malaysia Perlis.

# References

- [1] Murad, Sohiful Anuar Zainol, A. F. Hasan, A. Azizan, A. Harun, and J. Karim. "A concurrent dual-band CMOS low noise amplifier at 2.4/5.2 GHz for WLAN applications." *Indonesian Journal of Electrical Engineering and Computer Science (IJEECS)* 14, no. 2 (2019): 555-563. <u>https://doi.org/10.11591/ijeecs.v14.i2.pp555-563</u>

- [2] Aneja, Aayush, Xue Jun Li, and Peter Han Joo Chong. "Design and analysis of a 1.1 and 2.4 GHz concurrent dualband low noise amplifier for multiband radios." *Aeu-international Journal of Electronics and Communications* 134 (2021): 153654. <u>https://doi.org/10.1016/j.aeue.2021.153654</u>

- [3] Liu, Ya-ze, Wan-rong Zhang, Dong-yue Jin, Hong-yun Xie, Xin Huang, Ji-tian Chen, Yan-xiao Zhao, Shuo Liu, and Cheng-xiao Du. "A low power variable gain wideband low noise amplifier." In 2016 IEEE International Conference on Ubiquitous Wireless Broadband (ICUWB), p. 1-4. IEEE, 2016. <u>https://doi.org/10.1109/ICUWB.2016.7790410</u>

- [4] Shukla, Siddharth Shanker, Amrita Pandey, Sumit Kumar, Ali Hamza, and Gaurav Mehra. "90-nm dual-band CMOS LNA with gain enhancement for wireless LAN applications." In 2022 First International Conference on Electrical, Electronics, Information and Communication Technologies (ICEEICT), p. 1-5. IEEE, 2022. https://doi.org/10.1109/ICEEICT53079.2022.9768493

- [5] Jang, Junyoung, Hansol Kim, Geunhaeng Lee, and Tae Wook Kim. "Two-stage compact wideband flat gain lownoise amplifier using high-frequency feedforward active inductor." *IEEE Transactions on Microwave Theory and Techniques* 67, no. 12 (2019): 4803-4811. <u>https://doi.org/10.1109/TMTT.2019.2947483</u>

- [6] Luo, Yang, and Tongsheng Xia. "Design of reconfigurable low noise amplifier based on active inductor." In 2020 IEEE International Conference on Artificial Intelligence and Computer Applications (ICAICA), p. 977-982. IEEE, 2020. https://doi.org/10.1109/ICAICA50127.2020.9182454

- [7] Rafati, Maryam, Seyed Ruhallah Qasemi, Ali Nejati, and Parviz Amiri. "A 3.1-10.6 GHz forward body biased ultralow-voltage UWB LNA." In *2019 27th Iranian Conference on Electrical Engineering (ICEE)*, pp. 326-330. IEEE, 2019.

- [8] Sawayama, Yuito, Takayuki Morishita, Kiyotaka Komoku, and Nobuyuki Itoh. "Dual-band concurrent LNA with low gain deviation and low noise figure." In 2020 IEEE Asia-Pacific Microwave Conference (APMC), pp. 1006-1008. IEEE, 2020. https://doi.org/10.1109/APMC47863.2020.9331392

- [9] Khosravi, Hossein, Salman Zandian, Abolfazl Bijari, and Nabeeh Kandalaft. "A low power, high gain 2.4/5.2 GHz concurrent dual-band low noise amplifier." In 2019 IEEE 9th Annual Computing and Communication Workshop and Conference (CCWC), p. 0788-0792. IEEE, 2019. <u>https://doi.org/10.1109/CCWC.2019.8666621</u>

- [10] Sattar, Sami, and Tun Zainal Azni Zulkifli. "A 2.4/5.2-GHz concurrent dual-band CMOS low noise amplifier." IEEE Access 5 (2017): 21148-21156. <u>https://doi.org/10.1109/ACCESS.2017.2756985</u>

- [11] Datta, Sambit, Kunal Datta, Ashudeb Dutta, and Tarun Kanti Bhattacharyya. "A concurrent low-area dual band 0.9/2.4 GHz LNA in 0.13 μm RF CMOS technology for multi-band wireless receiver." In 2010 IEEE Asia Pacific Conference on Circuits and Systems, p. 280-283. IEEE, 2010. <u>https://doi.org/10.1109/APCCAS.2010.5774945</u>

- [12] Arshad, Sana, Faiza Zafar, Rashad Ramzan, and Q. Wahab. "Wideband and multiband CMOS LNAs: State-of-theart and future prospects." *Microelectronics Journal* 44, no. 9 (2013): 774-786. <u>https://doi.org/10.1016/j.mejo.2013.04.011</u>

- [13] Saberkari, Alireza, Saman Ziabakhsh, Herminio Martinez, and Eduard Alarcón. "Active inductor-based tunable impedance matching network for RF power amplifier application." *Integration* 52 (2016): 301-308. <u>https://doi.org/10.1016/j.vlsi.2015.07.013</u>

- [14] Malek, M. Ikram, and Suman Saini. "Improved two stage ultra-wideband CMOS low noise amplifier with out band rejection using low noise active inductor." In 2015 International Conference on Signal Processing and Communication Engineering Systems, p. 157-161. IEEE, 2015. <u>https://doi.org/10.1109/SPACES.2015.7058237</u>

- [15] Radha, Subramanyam, David Sundararaj Shylu, Perattur Nagabushanam, and Jisha Mathew. "Low noise amplifier with resistive and capacitive feedback for 2.4 GHz RF receiver front end." *Journal of High Speed Networks* 25, no. 2 (2019): 181-203. <u>https://doi.org/10.3233/JHS-190611</u>

- [16] Pandey, Ashutosh, and Ms Rajani Bisht. "Design of low power reconfigurable Ina for multiband receiver." In 2020 IEEE International Conference for Innovation in Technology (INOCON), p. 1-3. IEEE, 2020. https://doi.org/10.1109/INOCON50539.2020.9298217

- [17] Halim, N. F. A. B., S. A. Z. Murad, A. Harun, M. N. M. Isa, S. N. Mohyar, and A. Azizan. "Design of 3.1-6.0 GHz CMOS ultra-wideband low noise amplifier with forward body bias technique for wireless applications." In AIP Conference Proceedings, vol. 2203, no. 1. AIP Publishing, 2020. <u>https://doi.org/10.1063/1.5142114</u>

- [18] Wei, Chun, Ronghua Zhang, Zhiying Xia, Kui Cheng, Xinyu Liu, and Weijun Luo. "A concurrent dual-band low noise amplifier with gain enhancement topology for 2.4/5.2 GHz applications." *Informacije MIDEM* 52, no. 1 (2022): 11-16. <u>https://doi.org/10.33180/InfMIDEM2022.102</u>

- [19] Ibrahim, Abu Bakar, Nurul Husna Kahar, Hafizul Fahri Hanafi, Ashardi Abas, and Shamsul Arrieya Ariffin. "A new cascode low noise amplifier (LNA) with double feedback technique architecture for long term evolution (LTE) application." *Journal of Advanced Research in Applied Mechanics* 80, no. 1 (2021): 1-10. https://doi.org/10.37934/aram.80.1.110

- [20] Silva-Pereira, Marco, José T. de Sousa, João Costa Freire, and João Caldinhas Vaz. "A 1.7-mW- 92-dBm Sensitivity Low-IF Receiver in 0.13-\$\mu \$ m CMOS for Bluetooth LE Applications." *IEEE Transactions on Microwave Theory* and Techniques 67, no. 1 (2018): 332-346. <u>https://doi.org/10.1109/TMTT.2018.2876224</u>

- [21] Khosravi, Hossein, Abolfazl Bijari, Nabeeh Kandalaft, and Jorge Cabral. "A low power concurrent dual-band low noise amplifier for wlan applications." In 2019 IEEE 10th Annual Information Technology, Electronics and Mobile Communication Conference (IEMCON), p. 1118-1123. IEEE, 2019. <u>https://doi.org/10.1109/IEMCON.2019.8936211</u>

- [22] Kumar, Sudhanshu, Amar Nath Yadav, and Kavindra Kandpal. "Concurrent dual band CMOS LNA with improved IIP3 using modified DS technique." In 2022 IEEE International Symposium on Smart Electronic Systems (iSES), pp. 48-52. IEEE, 2022. <u>https://doi.org/10.1109/iSES54909.2022.00021</u>