Improved Domino Logic based Low Power CMOS Schmitt Trigger Circuit at Nano Scale Regime

DOI:

https://doi.org/10.37934/araset.57.2.4152Keywords:

Domino Logic, Leakage Current, Power Consumption, Robustness, Schmitt TriggerAbstract

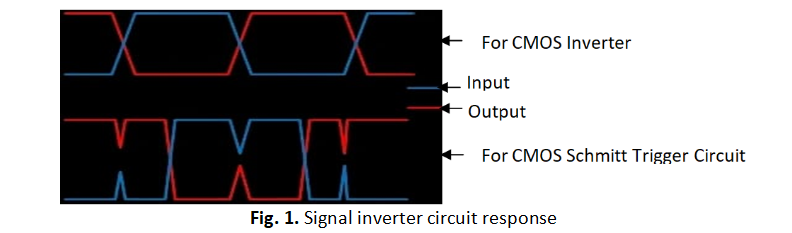

The requirement of high speed low power square wave generators that yield spike free signal enabled the design of Schmitt Trigger circuit. The designs BJT or FET based circuits have disadvantages like spikes in output signal cannot be suppressed, the output signal gain control is required, low packing density, considerable power dissipation, etc. This has paved way to development of CMOS based design. Further low power requirement enabled the CMOS based low power design aspects for the Schmitt Trigger circuit. The designs are modeled in DSCH and Microwind Tools for schematic and layout development at various technologies like 90nm, 65nm, 45nm and 32nm ad the designs are evaluated from HSPICE Tool. The choice of designs used are conventional domino logic, clock delayed domino keeper logic, clock delayed domino keeper logic with discharge path, foot driven stacked transistor logic, ground PMOS keeper logic, leakage current based logic, high speed domino logic and proposed clocked delayed dual keeper logic. The area is a trade-off parameter for proposed clocked delayed dual keeper design with an increase in area by atleast 9.8%. However the area occupied by conventional domino based Schmitt Trigger design is least due to usage of lesser number of transistors. The power dissipation is less for proposed clocked delayed dual keeper design by atleast 3.27%. However the power dissipation is least for Leakage Current based Schmitt Trigger design due to usage of lesser number of transistors.