Implementation of Two-Stage Multilevel Inverter System Using PIC Controller

DOI:

https://doi.org/10.37934/araset.28.2.4155Keywords:

Two-stage inverter, multilevel inverter, boost converter, Cascaded H-bridge, DC-DC converterAbstract

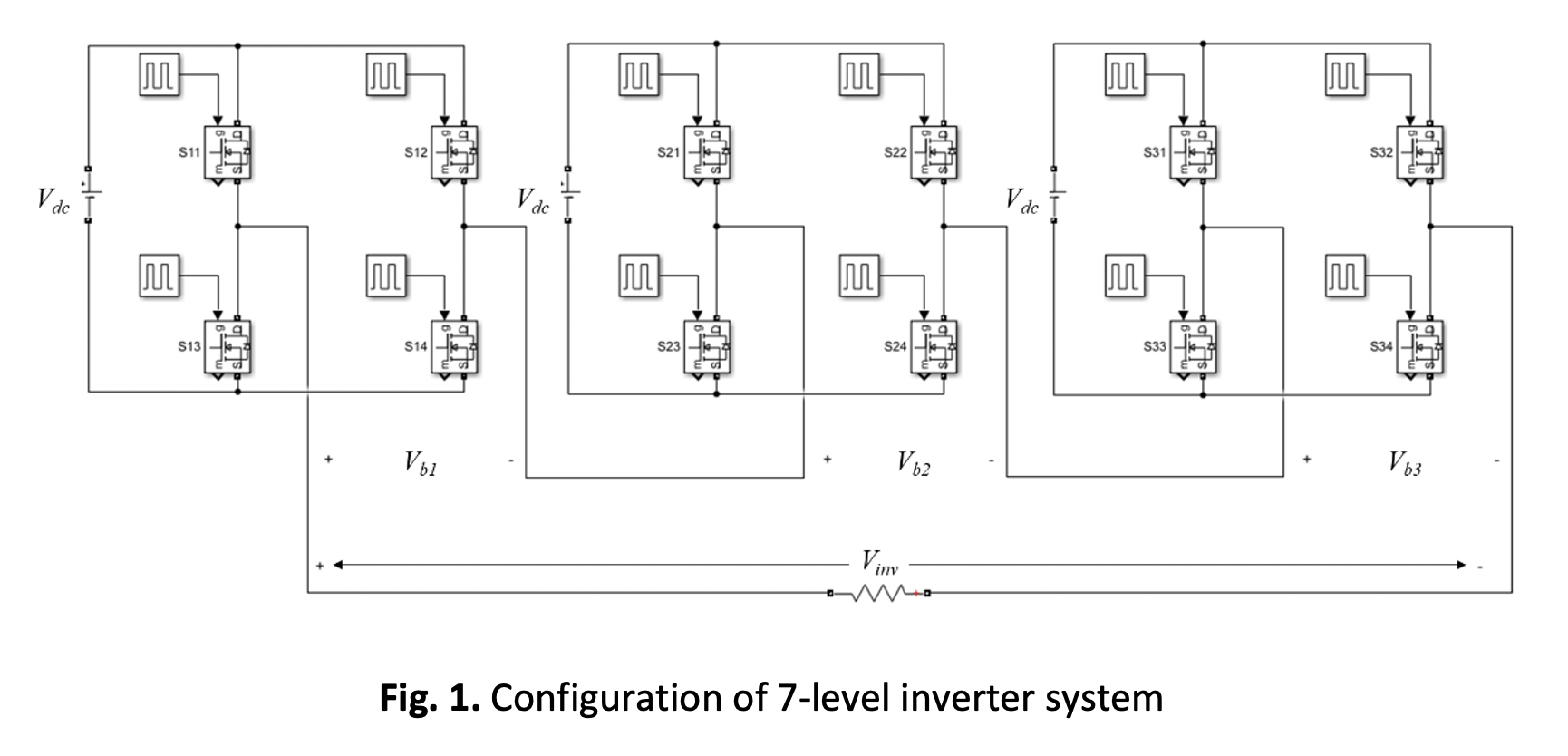

In this study, the Cascaded H-Bridge Multilevel Inverter (CMLI) is described for use with infrared dryer loads. Because of the low harmonic distortion content and reduced voltage stress in the switching devices, CMLI is one of particular interest. The CMLI topology and the Selective Harmonic Elimination Pulsed Width Modulation (SHEPWM) technology were studied and evaluated. To evaluate the inverter, SHEPWM modulation was studied and applied. The system also includes a DC-DC converter. The converter was designed to be used in infrared drying system powered by direct current (DC) power where an increased output voltage is required. This study also presented an evaluation of performance using infrared load of the CMLI based on power used at 100 W. As a result, a comparison of input power was made, and an assessment into the converter's power quality in terms of harmonic content and overall efficiency was conducted. The implementation of the system by hardware had been able to reduce the harmonic to 15.5%.

Downloads