Hardware Implementation of FIR Filter for ECG Signal Processing: Design, Optimization, and Performance Analysis on an FPGA

DOI:

https://doi.org/10.37934/araset.40.2.5061Keywords:

FIR Filter, FPGA, ECG Signal Processing, Hardware Accelerator, Kaiser Window, Digital FilterAbstract

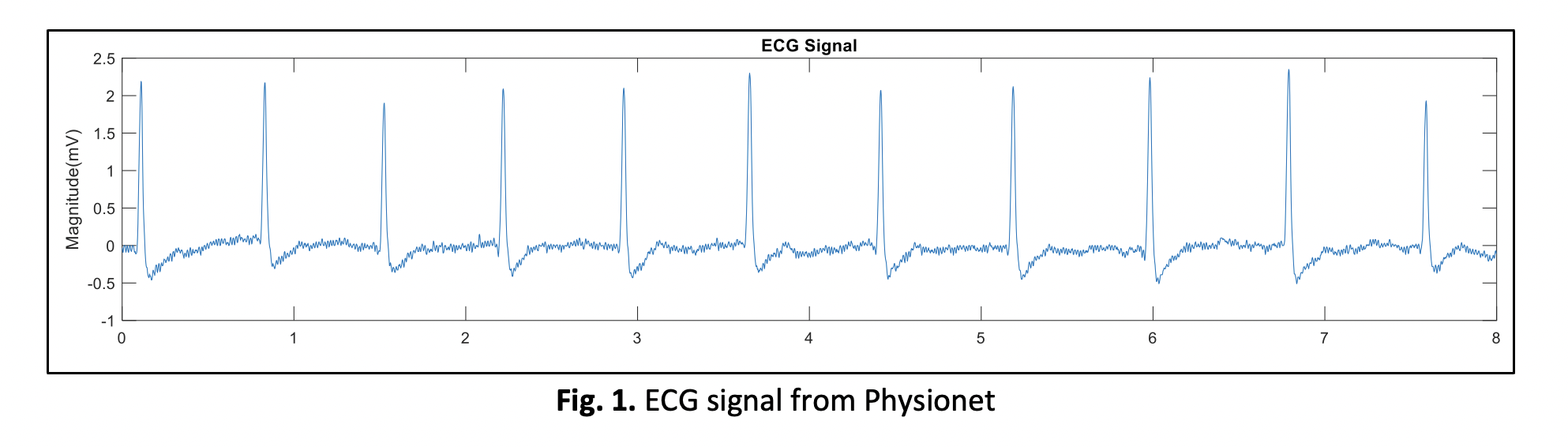

Electrocardiogram (ECG) signals are commonly used to diagnose heart-related diseases. However, noise induced during the measurement process can affect the accuracy of the diagnosis. Digital filters, such as the Finite Impulse Response (FIR) filter, are widely used to filter out noise from the ECG signal. Nevertheless, the processing speed of software-based FIR filters is slow for large ECG datasets due to serial processing. This paper presents a hardware implementation of the FIR filter for ECG signal processing to overcome the processing speed issue. The filter is designed using the Kaiser Window method and implemented on the Intel Cyclone IV Field Programmable Gate Array (FPGA). The filter is first designed in MATLAB to obtain the filter coefficients where the ECG data were obtained from Physionet database. From the difference equation, we designed the signal flow graph (SDFG) and then mapped into hardware logics to enable parallel processing. Simulation results of the software (MATLAB) and hardware (FPGA) implementations are obtained and compared. The results show that the FPGA-based FIR filter can process the ECG signal up to 1,250 times faster than software implementations. To further optimize the design and reduce hardware cost, we introduce optimized designs by applying the operation scheduling and constrained resource allocation techniques. The maximum operating frequency, logic utilization, and power consumption of each design were analysed and compared. This study demonstrates that custom-designed hardware logic for digital signal processing can significantly outperform software implementations due to its parallel processing capabilities. The proposed optimization techniques reduce the hardware cost while maintaining high processing speed and accuracy. The hardware implementation of the FIR filter for ECG signal processing has numerous applications in diagnosing heart-related diseases and real-time monitoring of ECG signals in critical care settings.

Downloads