Design of Low Power Control Unit for RISC-V Processor Core

DOI:

https://doi.org/10.37934/araset.60.2.265281Keywords:

RISC-V, Control unit, Low-power, Clock gatingAbstract

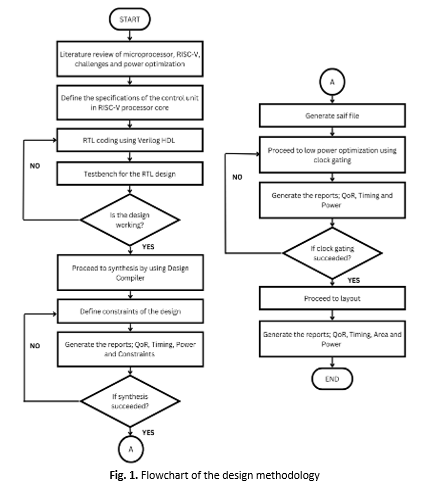

This research work focuses on the development of a low-power decode logic for a RISC-V processor core with specifications. The goal is to create a controller that performs all six groups of instruction formats outlined in the RV32I Base Integer Instruction Set. The control unit is designed to decode a total of 13 instruction sets, allowing for a comprehensive range of operations. A single instruction pipeline approach is implemented in the design to optimize performance. The synthesis of the design is carried out using the 32 nm standard library, resulting in a maximum operating frequency of 666.67 MHz. To further enhance power efficiency, clock gating techniques are employed, leading to a reduction in power consumption by 18.72 % from 112.15 µW to 91.45 µW. Additionally, the layout of the design is optimized, resulting in an area of 354.74 mm2. The successful development of this low-power decode logic demonstrates its potential for integration into larger RISC-V processor cores. Future enhancements can include expanding the instruction decoding capability to encompass the full range of 47 instructions in the RV32I Base Integer Instruction Set, as well as exploring additional pipeline stages to further improve performance. The results achieved in this project contribute to the ongoing pursuit of power-efficient and high-performance processor designs based on the RISC-V architecture.